Asksia.ai 的 Verilog 助手为数字电路设计提供全面支持。它提供即时解决方案、逐步解释和代码生成,帮助您进行语法检查、模块设计和调试。

适合。Asksia.ai 的 Verilog 助手专为各个水平的用户设计,包括初学者。它提供清晰的解释、语法指导和范例,帮助新手理解 Verilog 概念并提高编码技能。

可以。Verilog 助手能为各种数字电路生成代码片段和模板,包括组合逻辑和时序逻辑设计,帮助您启动项目或了解具体实现。

提供。Verilog 助手通过识别常见错误、建议修复并解释代码中的潜在问题来支持调试。此功能显著减少故障排除时间并提高代码质量。

可以。Asksia.ai 的 Verilog 助手非常适合 FPGA 设计项目。它能够协助 HDL 编码,提供综合优化,并在您的 Verilog 设计中就 FPGA 的具体考虑因素提供指导。

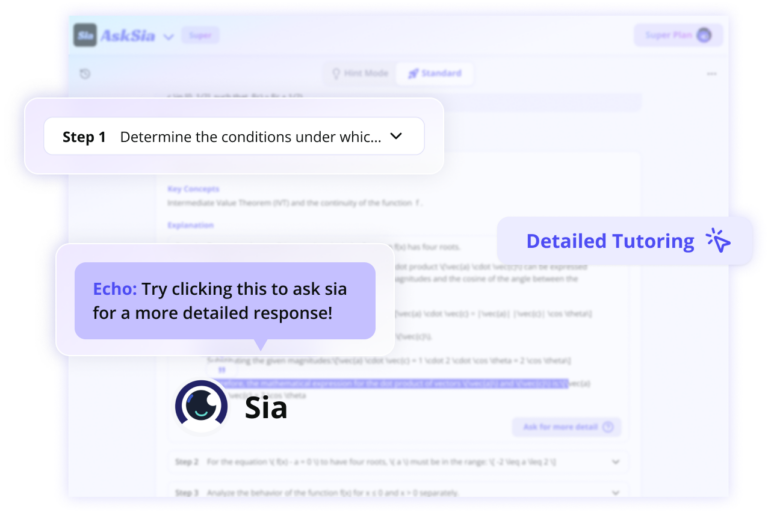

Asksia.ai 的 Verilog 助手以提供个性化的 AI 驱动支持而脱颖而出。它不同于静态资源,能够动态响应您的特定查询,提供实时代码生成和调试支持,使其更具互动性和个性化。

可以。Verilog 助手可协助您为设计创建测试平台。它为测试平台结构、激励生成和结果检验提供指导,帮助您为 Verilog 模块开发全面的验证环境。