Asksia.ai’s Verilog Helper provides comprehensive support for digital circuit design. It offers instant solutions, step-by-step explanations, and code generation for Verilog projects, helping you with syntax, module design, and debugging.

Yes. Asksia.ai’s Verilog Helper is designed to assist users at all levels, including beginners. It provides clear explanations, syntax guidance, and examples to help newcomers understand Verilog concepts and improve their coding skills.

Yes. The Verilog Helper can generate code snippets and templates for various digital circuits, including combinational and sequential logic designs, helping you kickstart your projects or understand specific implementations.

Yes. The Verilog Helper provides debugging support by identifying common errors, suggesting fixes, and explaining potential issues in your code. This feature can significantly reduce troubleshooting time and improve code quality.

Yes. Asksia.ai’s Verilog Helper is well-suited for FPGA design projects. It can assist with HDL coding, provide optimizations for synthesis, and offer guidance on FPGA-specific considerations in your Verilog designs.

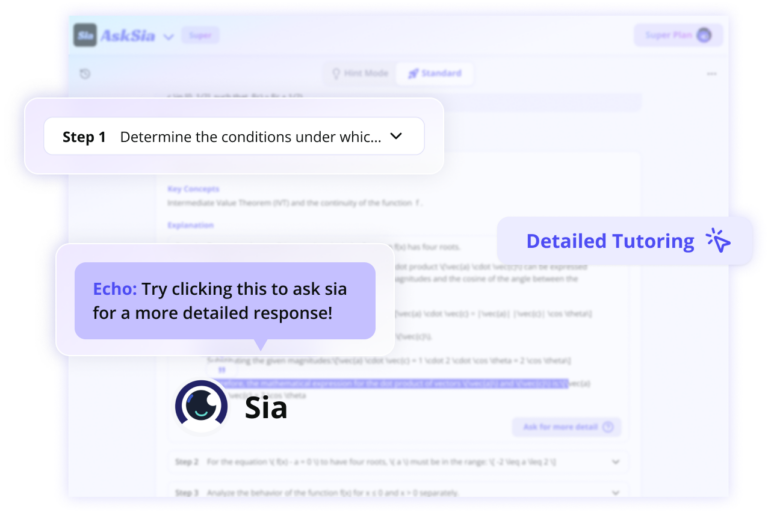

Asksia.ai’s Verilog Helper stands out by offering personalized, AI-driven assistance. Unlike static resources, it provides dynamic help, adapts to your specific queries, and offers real-time code generation and debugging support, making it more interactive and tailored to individual needs.

Yes. The Verilog Helper can assist in creating testbenches for your designs. It provides guidance on testbench structure, stimulus generation, and result checking, helping you develop comprehensive verification environments for your Verilog modules.