Asksia.aiのVerilogヘルパーは、デジタル回路設計を全面的にサポートします。即時ソリューション、ステップバイステップの説明、Verilogプロジェクト用のコード生成を提供し、構文、モジュール設計、デバッグを手助けします。

はい。Asksia.aiのVerilogヘルパーは、初心者を含むすべてのレベルのユーザーを支援するよう設計されています。新参者がVerilogの概念を理解し、コーディングスキルを向上させるための明確な説明、構文のガイド、および例を提供します。

はい。Verilogヘルパーは、組み合わせ論理および順序論理設計を含む様々なデジタル回路のコードスニペットやテンプレートを生成し、プロジェクトの開始や特定の実装を理解するのに役立ちます。

はい。Verilogヘルパーは、一般的なエラーの特定、修正の提案、およびコードの潜在的な問題の説明を通じてデバッグ支援を行います。この機能は、トラブルシューティングの時間を大幅に短縮し、コードの品質を向上させます。

はい。Asksia.aiのVerilogヘルパーはFPGA設計プロジェクトに非常に適しています。HDLコーディングの支援、合成の最適化、Verilog設計におけるFPGA特有の考慮事項へのガイダンスを提供します。

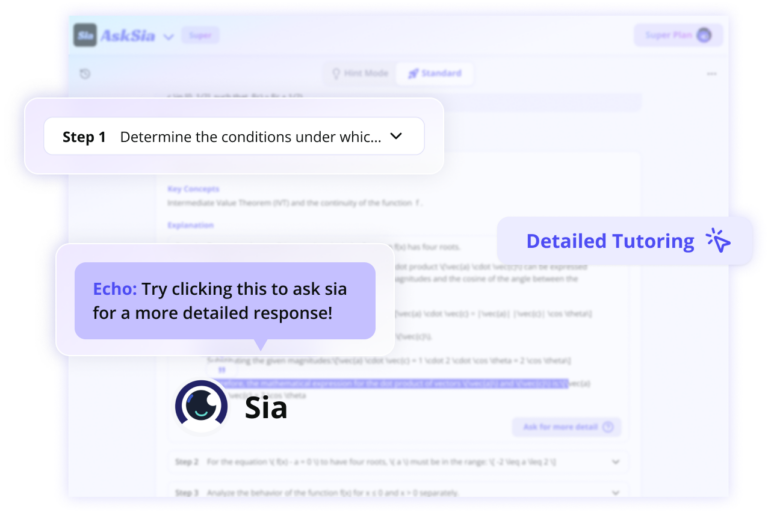

Asksia.aiのVerilogヘルパーは、個別のAI駆動の支援を提供することで際立っています。静的なリソースとは異なり、動的な支援を行い、特定の質問に応じて適応し、リアルタイムのコード生成とデバッグサポートを提供するため、よりインタラクティブで個別のニーズに合わせたものとなっています。

はい。Verilogヘルパーは、設計用のテストベンチ作成を支援します。テストベンチの構造、刺激生成、および結果確認に関するガイダンスを提供し、Verilogモジュールのための包括的な検証環境を開発するのを支援します。