Der Verilog-Helfer von Asksia.ai bietet umfassende Unterstützung für die Entwicklung digitaler Schaltungen. Er liefert sofortige Lösungen, schrittweise Erklärungen und Code-Generierung für Verilog-Projekte, hilft bei Syntax, Modulentwurf und Debugging.

Ja. Der Verilog-Helfer von Asksia.ai ist darauf ausgelegt, Nutzer auf allen Ebenen zu unterstützen, einschließlich Anfängern. Er bietet klare Erklärungen, Hilfe bei der Syntax und Beispiele, um Neulingen die Verilog-Konzepte näherzubringen und ihre Programmierfähigkeiten zu verbessern.

Ja. Der Verilog-Helfer kann Code-Snippets und Vorlagen für verschiedene digitale Schaltungen generieren, einschließlich kombinatorischer und sequentieller Logikdesigns, und hilft Ihnen, Ihre Projekte zu starten oder spezielle Implementierungen zu verstehen.

Ja. Der Verilog-Helfer bietet Unterstützung beim Debugging, indem er häufige Fehler identifiziert, Lösungsvorschläge macht und potenzielle Probleme im Code erklärt. Diese Funktion kann die Fehlersuche erheblich verkürzen und die Codequalität verbessern.

Ja. Der Verilog-Helfer von Asksia.ai ist bestens geeignet für FPGA-Designprojekte. Er kann beim HDL-Coding helfen, Optimierungen für die Synthese bieten und Richtlinien für FPGA-spezifische Überlegungen in Ihren Verilog-Designs geben.

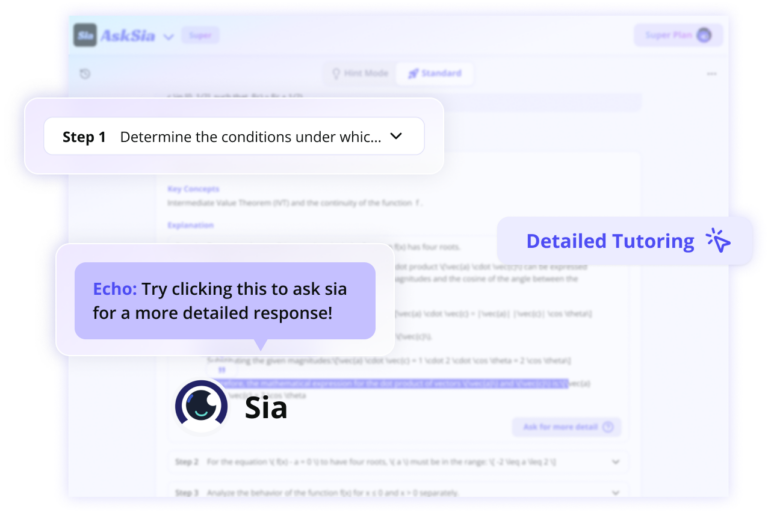

Der Verilog-Helfer von Asksia.ai sticht durch personalisierte, KI-gesteuerte Unterstützung hervor. Anders als statische Ressourcen bietet er dynamische Hilfe, passt sich Ihren spezifischen Fragen an und liefert Echtzeit-Codegenerierung und Debugging-Unterstützung, was ihn interaktiver und individueller gestaltet.

Ja. Der Verilog-Helfer kann bei der Erstellung von Testbenches für Ihre Designs unterstützen. Er bietet Anleitungen zur Struktur von Testbenches, zur Generierung von Teststimuli und zur Ergebniskontrolle, um Ihnen zu helfen, umfassende Verifikationsumgebungen für Ihre Verilog-Module zu entwickeln.